PCIe 6.0 Specification Hits Version 0.5: On Track for 2021

by Anton Shilov on February 21, 2020 10:00 AM EST- Posted in

- Interconnect

- PCIe

- PCI-SIG

- PCIe 6.0

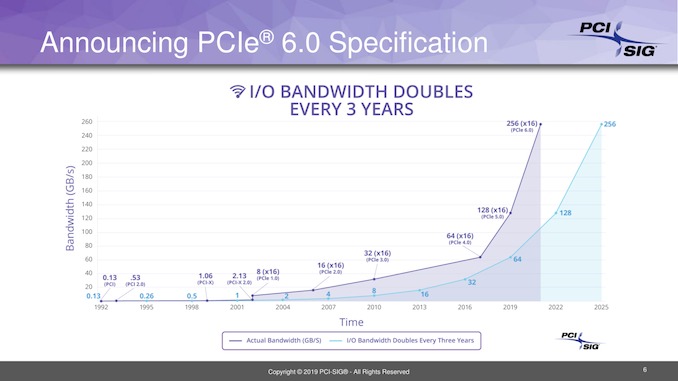

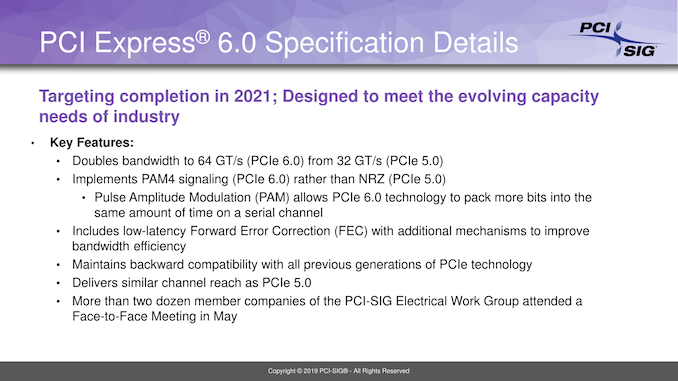

PCI-SIG has released version 0.5 of the PCIe 6.0 specification to its members this week. The new, "first draft" version of the spec includes the feedback the group got from its members after publication of version 0.3 back in October. With their latest update, PCI-SIG remains confident that it is on track to finalize the PCIe 6.0 standard in 2021.

It took PCI-SIG long seven years to complete the PCIe 4.0 specification, a long slog that the group has committed to avoiding going forward for PCIe 5.0 and beyond. With PCIe 6.0, PCI-SIG is keeping up that rapid pace of development, releasing the first draft version of the spec less than a year after formal announcement of the spec.

Overall, PCI-SIG has five key steps in creating a PCIe specification:

- Version 0.3 is beheld as a Concept and outlines the key features and architecture of the technology. In case of PCIe 6.0, we are talking about 64 GT/s per lane speed, pulse amplitude modulation with 4 levels (PAM-4) encoding, and forward error correction (FEC).

- Version 0.5 is considered as the First Draft specification and so it covers all the key aspects of the architecture and includes feedback from interested parties (within PCI-SIG) to version 0.3. Members of the group will be able to add new functionality to the technology at this point.

- Version 0.7 is deemed to be the Complete Draft, everything has to be defined at all levels and electrical specifications must have been validated via test chips. No new features may be added after release of this iteration of the specification.

- Version 0.9 is the Final Draft that is meant to allow PCI-SIG members to review the technology for their intellectual property.

- Version 1.0 is the Final Release.

The publication of version 0.5 of the PCIe 6.0 specification is essentially the final call for submissions of the new features by PCI-SIG member companies. Furthermore, with the first draft available, companies can start designing test silicon to ensure that everything works and even begin preliminary work on commercial chips.

The next milestone for the PCIe 6.0 specification will be the upcoming PCI-SIG Developers Conference 2020 in early June, where the group plans to present deep dives into the features of the technology.

Related Reading:

- PCIe 6.0 Dev Reaches v0.3; On-Track for a Full Specification In 2021

- PCI Express Bandwidth to Be Doubled Again: PCIe 6.0 Announced, Spec to Land in 2021

- Gen-Z PHY Specification 1.1 Published: Adds PCIe 5.0, Gen-Z 50G Fabric

- PCI-SIG Finalizes PCIe 5.0 Specification: x16 Slots to Reach 64GB/sec

- Synopsys Demonstrates CXL and CCIX 1.1 over PCIe 5.0: Next-Gen In Action

Source: PCI-SIG

74 Comments

View All Comments

fred666 - Friday, February 21, 2020 - link

Given the slow adoption of PICe 4.0, I doubt we will really be at PCIe 6.0 by 2021. Except maybe some niche products.UltraWide - Friday, February 21, 2020 - link

They can skip versions to the latest, there is no rule that requires sequential implementation. :)mode_13h - Friday, February 21, 2020 - link

Since 6.0 builds on 5.0, I think it's more realistic to expect most vendors not to skip.p1esk - Friday, February 21, 2020 - link

5.0 is dead. I'm not going to buy 5.0 when I know 6.0 is around the corner.Sivar - Friday, February 21, 2020 - link

You should wait for PCIe 7.0. What possible real-world use could links with a mere 128GB/s or 256GB/s have?p1esk - Friday, February 21, 2020 - link

Just because you can't think of any real-world use cases, does not mean they don't exist. For me it would be very important to increase bandwidth between my Quadro cards (currently I have to use NVlink between pairs of cards).FreckledTrout - Friday, February 21, 2020 - link

LOL yeah but even PCIe 4.0 would do the trick for you let alone PCIe 7 :)rpg1966 - Saturday, February 22, 2020 - link

And if you need moar, then surely double or quadruple whatever you have now, is better than waiting forever for 8x whatever you have now.MDD1963 - Tuesday, February 25, 2020 - link

If I need more bandwidth than that offered by PCI-e 4.0, I will simply download more! :)mode_13h - Saturday, February 22, 2020 - link

It doesn't matter if you can think of a use case, if the technology is too expensive or impractical to implement for your market segment.