TSMC Outlines 2nm Plans: N2P Brings Backside Power Delivery in 2026, N2X Added To Roadmap

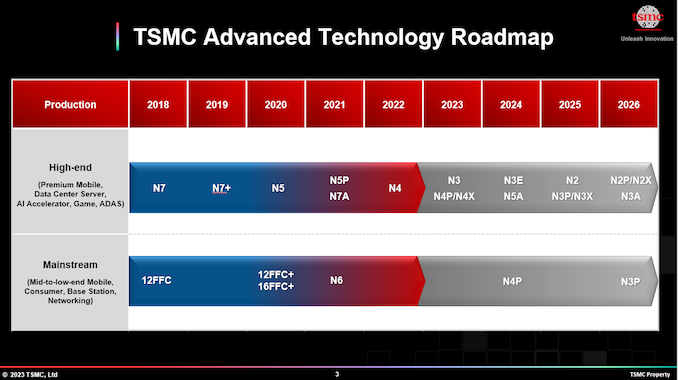

by Anton Shilov on April 26, 2023 3:10 PM ESTAt its 2023 North American Technology Symposium today, TSMC has disclosed additional details about its plans for its forthcoming N2 2nm-class production nodes in 2025 – 2026 and beyond. TSMC's N2 family of fabrication technologies will be expanding with additional variations, including N2P with backside power delivery, and N2X for high-performance computing. Between these forthcoming N2 generation process nodes, TSMC is laying out a roadmap to continue their relentless pace of increasing transistor performance efficiency, optimize power consumption, and improving transistor density.

N2 Gets Denser

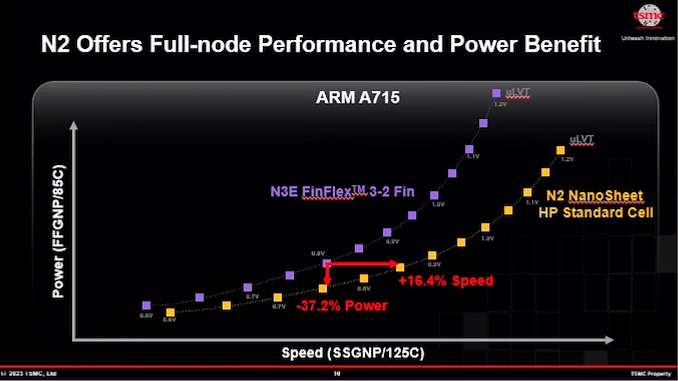

TSMC's initial N2 manufacturing process, which was introduced last year, will be the foundry's first node to use gate-all-around (GAAFET) transistors, which TSMC is calling Nanosheet transistors. GAAFET's advantages over current FinFET transistors includes lowered leakage current (as gates are present on all four sides of the channel), as well as the ability to adjust channel width for higher performance or lower power consumption.

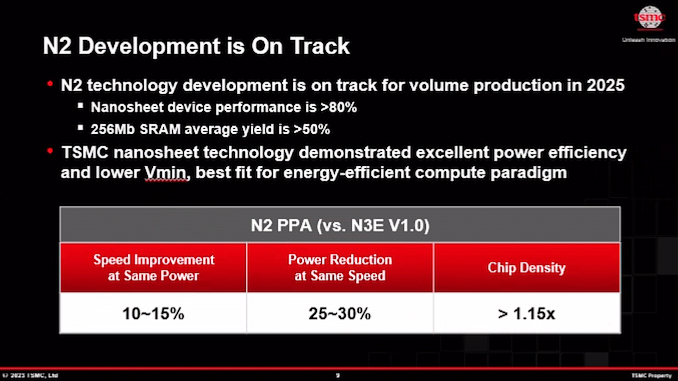

When introducing this technology last year, TSMC said that it would enhance transistor performance by 10% to 15% with the same power and complexity, or reduce power consumption by 25% to 30% at the same clock and transistor count. The company also says that N2 will offer 'mixed' chip densities of over 15% greater than N3E, which is an increase from the 10% density increase announced last year.

Today, the company said that N2 technology development is on track and the node will enter high-volume production in 2025 (probably very late 2025). The company also said that its Nanosheet GAA transistor performance is achieving better than 80% of its target specifications two years before entering HVM, and that average yield of a 256Mb SRAM test IC is over 50%.

"TSMC nanosheet technology demonstrated excellent power efficiency and lower Vmin, best fit for energy-efficient compute paradigm," a statement by TSMC reads.

| Advertised PPA Improvements of New Process Technologies Data announced during conference calls, events, press briefings and press releases |

|||||

| TSMC | |||||

| N5 vs N7 |

N3 vs N5 |

N3E vs N5 |

N2 vs N3E |

||

| Power | -30% | -25-30% | -34% | -25-30% | |

| Performance | +15% | +10-15% | +18% | +10-15% | |

| Chip Density* | ? | ? | ~1.3X | >1.15X | |

| Volume Manufacturing |

Q2 2022 | H2 2022 | Q2/Q3 2023 | H2 2025 | |

*Chip density published by TSMC reflects 'mixed' chip density consisting of 50% logic, 30% SRAM, and 20% analog.

N2P Gets Backside Power Delivery In 2026

TSMC's N2 family will evolve and sometime in 2026, when the company plans to introduce its N2P fabrication technology. N2P that will add backside power rails to N2's Nanosheet GAA transistors.

Backside power delivery is meant to decouple I/O and power wiring by moving power rails to the back, addressing challenges like elevated via resistances in the back-end-of-line (BEOL). This, in turn, will enhance transistor performance and reduce their power consumption. Also, backside power deliver eliminates some potential interference between data and power connections.

Backside power delivery is innovation whose importance is hard to overstate. Chipmakers have been fighting resistances in chip power delivery circuitry for years, and backside power delivery networks (PDN) are a yet another method to address them. In addition, decoupling PDN and data connections also helps with area reduction, so expect N2P to further increase transistor density compared to N2.

For now, TSMC is not disclosing any hard numbers regarding N2P's performance, power, and area (PPA) advantages over N2. But based on what we hear from industry sources, backside power rails alone could bring a single digit power improvements and double-digit transistor density improvements.

TSMC says that N2P is on track to be production ready in 2026, so we can speculate that the first N2P-based chips will be available in 2027. This timeline would put TSMC roughly two years behind rival Intel when it comes to backside power, assuming they're able to ship their own 20A process on time in 2024.

N2X: Even More Performance

In addition to N2P, which will likely be a working horse of TSMC's 2nm generation of processes, TSMC is also prepping N2X. This will be a fabrication process tailored for high-performance computing (HPC) applications like high-end CPUs, which need increased voltages and clocks. The foundry is not outlining the specific advantages this node will compared to N2, N2P, and N3X, but as with all performance-enhanced nodes, the actual benefits are expected to depend signficantly on how much design technology co-optimization (DTCO) is practiced.

38 Comments

View All Comments

my_wing - Friday, April 28, 2023 - link

So on time that in Apr 2023 you still did not see any N3 product and that is your on time.TSMC N3 is CANCEL and N3E which is less density to N3 still on track.

That Intel Accountant CEO is rubbish but under PAT it can be late but not this, intel 4 is ramping, it does take 6 months from ramp to real product on the market, I think it did entered risk production back 2H 2022, so it did not slip.

Zoolook - Sunday, April 30, 2023 - link

In that case we'll see Meteor Lake in July!I doubt it though, lately second half of the year means we'll scramble to launch before christmas.

Kamen Rider Blade - Saturday, May 6, 2023 - link

Proof is in the mass produced product, so until Intel delivers on it, it's just promises.caribbeanblue - Tuesday, May 2, 2023 - link

That's chip/core density with non-logic components included on a Cortex-A72 afaik, N3E chip density improvement is 1.3x while the logic density is 1.6x. N3E no denser for cache than N5.Tuna-Fish - Friday, April 28, 2023 - link

> that would be even more TSVs than having the power within the power chiplet and sinking data connections to the cacheWhat makes you think that? You make the bottom chiplet on an older process and power it from below, and the CPU from above. The only TSVs needed are the data connections from the cpu to the cache, on the chiplet that holds the cache.

> and that's also missing the even bigger problem that all the IO connections would also have to go through the cache

This is desirable. The vast majority of IO operations that the cpu does check cache first. The proportion of uncached (mostly PCIe) accesses is tiny compared to normal memory lookups.

quaz0r - Wednesday, May 10, 2023 - link

"This timeline would put TSMC roughly two years behind rival Intel when it comes to backside power, assuming they're able to ship their own 20A process on time in 2024."🤡

Santoval - Saturday, May 27, 2023 - link

All three PPA metrics are a bit disappointing for a brand new FET tech.I expected better values...

Oxford Guy - Wednesday, June 7, 2023 - link

How many nm is 2nm these days?