GlobalFoundries Weds FinFET and SOI in 14HP Process Tech for IBM z14 CPUs

by Anton Shilov on September 22, 2017 7:00 AM EST- Posted in

- CPUs

- GlobalFoundries

- IBM

- Semiconductors

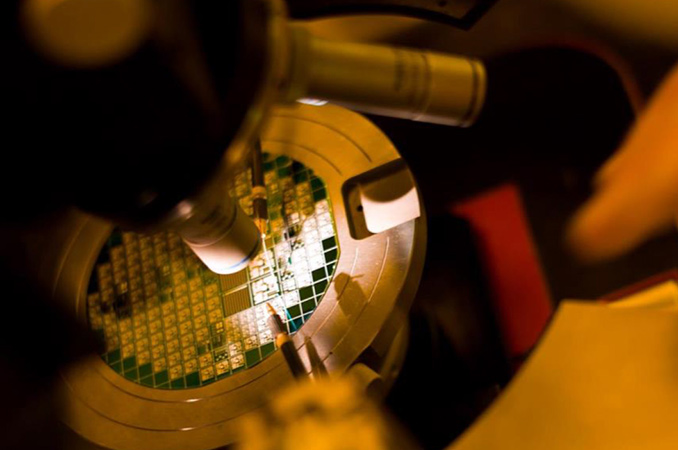

GlobalFoundries this week formally introduced its new custom process technology that will be used to manufacture IBM's z14 CPUs, which in turn were announced earlier this year. The 14HP (14 nm, high performance) tech weds FinFET transistors and SOI substrates to get IBM the best of both worlds: small feature sizes and maximized clockspeed potential.

When IBM and GlobalFoundries agreed to transfer semiconductor manufacturing business of the former to the latter, IBM demanded GF to develop and offer custom fabrication processes for IBM’s server CPUs throughout 2014 to 2024 timeframe and involving multiple nodes. Initially the companies talked about custom 22 nm, 14 nm and 10 nm technologies, but in their final announcement they only mentioned a 10-year exclusive supply agreement without disclosing particular nodes. Therefore, it remains to be seen what GlobalFoundries, which is skipping the 10 nm node, is going to offer to its partner (a custom 7 nm is a natural guess). Earlier this year IBM announced its z14 processors for mainframes and this week GlobalFoundries disclosed details about the process technology used to make these chips.

Before we proceed to 14HP, let’s recap what is the IBM z14 and why the blue giant needed a custom technology to build it. The IBM Z mainframes are designed for 24/7/365 availability with zero downtime and are aimed at mission critical applications like credit card processing. IBM Z mainframes are based on specially designed IBM z-series CPUs, which are unique both in terms of microarchitecture, feature set and even physical layout. Each IBM Z14 blade features six CPUs (which IBM calls CPs) carrying processing cores and L2+L3 caches as well as a system control chip (which IBM calls SC) featuring a large L4 cache as well as various interconnects. Each IBM z14 SC CPU consists of 6.1 billion transistors, runs at 5.2 GHz and contains 10 cores with dedicated 6 MB L2 per core (2MB L2 for instructions, 4MB L2 for data) and 128 MB shared L3. Meanwhile, the system control (SC) chip consists of 9.7 billion transistors and features 672 MB of L4 and interconnects to ensure coherency between CPUs. Needless to say, that both CP and SC are extremely complex and benefit from manufacturing technologies with small feature sizes.

Being very complex and very fast, IBM’s CPUs for z-series mainframes were historically produced using custom fabrication processes that were architected to deliver maximum performance, manufacturing costs be damned. In fact, it was IBM whom first used SOI substrates to build its RS64-IV codenamed ‘Istar’ PowerPC-AS CPUs in 2000, which was then followed by AMD and others whom used SOI to build their own highly-successful processors. The use of SOI enables a tangible increase of CPU clock rates without a massive increase of power consumption, but a SOI wafer substrate costs more than a bulk substrate, so this is exactly what GlobalFoundries’14HP is about.

| Comparison of 14 nm Branded Process Technologies | |||||||

| GlobalFoundries 12LP |

GlobalFoundries 14HP |

GlobalFoundries 14LPP ? |

TSMC 16FF |

Intel 14nm |

|||

| Fin Pitch | ? | ? | ? | ? | 42 nm | ||

| Gate Pitch | ? | ? | 78 nm | 90 nm | 70 nm | ||

| Min Metal Pitch | ? | ? | 64 nm | 64 nm | 52 nm | ||

| Gate Height | ? | ? | less than 480 nm | 480 nm | 399 nm | ||

| Metal Layers | 13 | 17 | 13 | unknown | unknown | ||

| Design Library | 7.5T | 12T | 9T | 9T | unknown | ||

GlobalFoundries says that the 14HP process technology leverages “the proven 14nm FinFET high-volume experience of our Fab 8 facility”, but does not explicitly say that 14HP is based on 14LPP; only that it uses SOI substrates instead of bulk ones. In fact, looking at the numbers it appears to be substantially different. When compared to GF’s 14LPP and similar bulk FinFET process technologies, 14HP can support up to 17 metal layers (vs. 13 for the 14LPP) and uses 12T libraries (vs. 9T and 7.5T for various 14 nodes). As for experience, 14HP will be utilized across the same ASML TWINSCAN NXT scanners that the company uses to produce existing chips using its current FinFET technologies.

GlobalFoundries is not disclosing too many specific details about 14HP, which isn't all that surprising given the situation at hand. There is a single customer that is going to use it, and IBM does not want to share too many details about how it designs its processors as well. So, while we do understand that SOI can help with increasing frequencies and voltages compared to bulk process technologies, we do not have precise numbers here.

Related Reading:

- Hot Chips: IBM's Next Generation z14 CPU Mainframe Live Blog (5pm PT, 12am UTC)

- GlobalFoundries and AMD Announce First 14nm FinFET Sample Production Success

- GlobalFoundries Adds 12LP Process for Mainstream and Automotive Chips; AMD Planning 12LP CPUs & GPUs

- GlobalFoundries Details 7 nm Plans: Three Generations, 700 mm², HVM in 2018

- GlobalFoundries to Expand Capacities, Build a Fab in China

- GlobalFoundries Updates Roadmap: 7 nm in 2H 2018, EUV Sooner Than Later?

Source: GlobalFoundries

31 Comments

View All Comments

saratoga4 - Friday, September 22, 2017 - link

>This is the second time I've seen a comment about #T libraries in a recent process update article. What exactly does it mean?T = "Track". Rather than just looking at how big each individual fin is in a FinFET transistor, you also have to consider how large each logic cell is (how many fins and metal contacts it will require). Even if the fins stay the same size, if you can make each one more capable, you can make the logic cell smaller by using fewer fins and/or metal wires.

name99 - Friday, September 22, 2017 - link

Here's a very simple explainer.Each fin of a finFET can carry a limited amount of current (which is usually not as much as is needed). This means multiple fins are required to create a single transistor. In the past this was as much as 4 fins per transistor (more for some specialty high-current transistors), and a focus of recent design has been to make the fins taller, which allows them to carry less current, thus reducing the number required (most of the time) to three fins, then two, and ultimately one.

Each stage of being able to reduce the number of fins means that you can rearrange (and shrink) the various items required to create standard cells (like a single bit of an SRAM).

There's always been some variation in how SRAMs are designed and laid out (in the past people talked about 6T vs 8T designs, T in that case meaning the number of transistors), but this issue of "track size of an SRAM bit" has become a bigger issue since FinFETs because each time you can make the fins taller and reduce the number per transistor, you get an additional density boost.

I assume that IBM's using these high-track-number cells means, essentially, they want lots of fins for each transistor creating higher currents, which in turn allows for faster switching, at the cost of more power.

(There is a second set of issues related to how the metal layers per cell are laid out connecting the various pieces together, but the above gives the idea and the main concerns.)

CajunArson - Friday, September 22, 2017 - link

Thanks!evancox10 - Friday, September 22, 2017 - link

Not sure this is really correct. The std cell track height has nothing to do with SRAM, which has a completely different design/layout. (Although yes, the T in 6T SRAM does stand for transistor.)The track height is simply a dimensionless measure of the height of the standard cells used in a given library. (Note that there are almost always multiple libraries available for a given process, although with smaller nodes the development of the process and the std cell libraries has become more tightly coupled.) If a given library has cells that are 120 nm tall, and the M1 pitch is 10 nm then you have a 120 nm / 10 nm = 12 Track cell. This measure is used instead of the raw height because it scales with the process node shrinks, so we can talk about a 12 T cell in 10 nm and also 90 nm and still (kind of) mean the same thing. (The absolute performance difference would of course be huge.) In both of these you could route 12 separate metal lines horizontally through the cell. In reality, you get fewer than 12 because power and ground are routed in a solid stripe along the top and bottom of the rows.

Typically from what I've seen, 7 T or less is for the densest (aka cheapest) designs, 7-10 is middle of the road, and 10+ for high performance. I'm not an expert in cell design, so I can't really say why larger cells give you more performance. It definitely gives the cell designer more area to work with. You additional vertical area, and can still use as much width as needed. Because unlike height, width is variable from cell to cell.

FreckledTrout - Friday, September 22, 2017 - link

Does the SOI cost that much more that AMD choose to use the 14LPP process over the 14HP process to make Zen cores? Just curious as it seems very likely they could have increased frequency due to how efficient the CPU's are.saratoga4 - Friday, September 22, 2017 - link

The wafers are a lot more expensive, yeah.MrSpadge - Saturday, September 23, 2017 - link

It's not that much more expensive (see 1st post). But I'm sure the process wasn't ready for Zen & Vega they only start to talk about it now. The regular 14 nm process was licensed from Samsung and freshly implemented when AMD already needed it (at decent yields, of course).Brodz - Wednesday, September 27, 2017 - link

Well that must hold true because AMD have mostly always used SOI, right up to Piledriver.Not sure entirely how different it is though from the 14LPP process, but it seems like AMD are moving forward with 12nm and then 7nm FinFET. Either it requires too much time or cost to rework Zen, process itself costs too much, a combination of those three, or IBM won't let them use it.

FunBunny2 - Friday, September 22, 2017 - link

-- IBM Z mainframes are based on specially designed IBM z-series CPUs, which are unique both in terms of microarchitecture, feature set and even physical layout.there are billions and billions of lines of COBOL which depend on hardware assists implemented decades ago. and there are, likely, millions of lines of assembler running all manner of critical systems.

phoenix_rizzen - Friday, September 22, 2017 - link

From the article:"Each IBM z14 SC CPU consists of 6.1 billion transistors, runs at 5.2 GHz and contains 10 cores with dedicated 6 MB L2 per core (2MB L2 for instructions, 4MB L2 for data) and 128 MB shared L3. Meanwhile, the system control (SC) chip consists of 9.7 ..."

Shouldn't that first "Z14 SC CPU" be "Z14 CP CPU"?

Was really confused reading that wondering why the system control chip had 10 cores with no mention of the actual CP setup. Then the next sentence is about the SC again, with different specs.