The Intel Broadwell-E Review: Core i7-6950X, i7-6900K, i7-6850K and i7-6800K Tested

by Ian Cutress on May 31, 2016 2:01 AM EST- Posted in

- CPUs

- Intel

- Enterprise

- Prosumer

- X99

- 14nm

- Broadwell-E

- HEDT

Turbo Boost Max 3.0 (TBM3), aka Turbo Boost Max or Turbo Boost 3.0

When Intel released the enterprise focused Broadwell-EP Xeon CPUs, there were a few features added to the platform over the previous Haswell-EP generation. One of these has come through to the consumer parts, though in a slightly different form.

For Broadwell-EP, one of the new features was the ability to have each core adjust the frequency independently depending on AVX or non-AVX workloads. Previously when an AVX load was detected, all the cores would reduce in frequency, but beginning with BDW-EP now they act separately. Intel has taken this enterprise feature and expanded it a little into a feature they're calling ‘Turbo Boost Max 3.0’.

Turbo Boost 2.0 is what Intel calls its maximum Turbo or ‘peak’ frequency. So in the case of the i7-6950X, the base frequency is 3.0 GHz and the Turbo Boost 2.0 frequency is 3.5 GHz. The CPU will use that frequency when light workloads are in play and decrease the frequency of the cores as the load increases in order to keep the power consumption more consistent. Turbo Boost 2.0 frequencies are advertised alongside the CPU on the box - TBM3 will be slightly different and not advertised.

TBM3, in a nutshell, will boost the frequency of a single CPU core when a single-threaded program is being used.

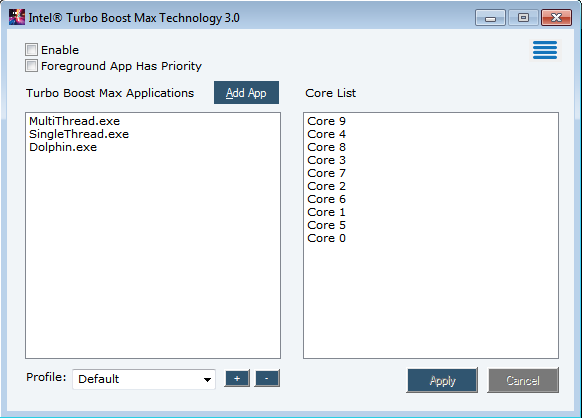

It requires a driver, similar to Skylake’s Speed Shift feature (which is not in Broadwell-E), which should be distributed in new X99 motherboard driver packages, but will also be rolled out in Windows 10 in due course. It also comes with a user interface, which might make it easier to explain:

Each of the cores in the processor can be individually accessed by the OS with the new driver, and the cores will be rated based on their performance and efficiency as they come out of Intel. In the image above, Core 9 is rated the best, with Core 0 at the bottom. This means that for TBM3, the driver will primarily use Core 9.

When enabled, TBM3 will activate in two modes: either the foreground application, or from a priority list. For the foreground selection, when the software detects a single threaded workload in play, it will attempt to pin the software to the best core (similar to changing the affinity in task manager to one core), and then boost the frequency. In priority mode, the application will look for any application on the left-hand panel (which has to be added manually). If an application with higher priority is present, then the software will unpin the current software and take the higher priority one and pin that instead.

When pinned, the software will boost the frequency of that core only. The only question now is how much is the boost, and what is the effect on performance? Unfortunately, both of those questions have bad answers.

Intel refuses to state the effect of TBM3, saying that ‘each CPU is different and could boost by different amounts’. Now, you might think that makes sense. However…

Turbo Boost Max 3.0 has to be supported by the motherboard manufacturer in the BIOS. The TBM3 settings have to be set in the BIOS, which means that the usefulness of such a feature is actually down to the motherboard manufacturers. But they know how to do it right, right? Well, here’s where it can get worse.

On the MSI motherboard we used for most of our testing, Turbo Boost Max 3.0 was disabled by default in the BIOS. We asked about this, and they said it was a conscious decision made by management a couple of weeks prior. This makes TBM3 useless for most users who never even touch the BIOS. That sounds good, right?

Well, the BIOS also sets how much the CPU can boost by. So ultimately it doesn’t matter how much the CPU might like to boost in frequency, the system will only boost by the amount it says so in the BIOS, which is set by the motherboard manufacturer. In the case of the MSI BIOS, it was set to ‘Auto’. In my case, ‘Auto’ meant a boost of zero, despite the MSI BIOS ‘suggesting’ 4000 MHz. I had to manually set Core 9 to a 40x multiplier. Then it worked.

All in all, TBM3 was only enabled after I changed two settings and specifically setting the correct core in the BIOS. For me, this isn’t a global feature if that is the case. That’s not to mention how Multi-Core Turbo also comes into the mix, which still works with Turbo Boost 2.0 speeds by default. Based on what we've seen, it would seem at this time that TBM3 isn’t being readily embraced at this time.

It should be noted that we also had one of the new ASUS motherboards in for testing, however time was too limited before leaving for Computex to verify if this is the case on the ASUS motherboard as well. ASUS has told me that they have/will have a software package that enables TBM3 to be applied to multiple cores at once, whereas the Intel software will only accelerate a single program. It should be interesting to test.

The Reviewers Problem With Turbo Boost Max 3.0

In the options menu for TBM3, there are two primary options to take note of. The first is the utilization threshold, which is the % at which the software will take control of the single threaded application and pin it to a core. By default, this is set at 90%.

The other option is where a dilemma will be faced. It is the evaluation interval, or the period of time between checks that the software makes in order to accelerate a program. The version of the software we had started with a value of 10 seconds. That means if the software package starts one second or nine seconds into a benchmark run, it can affect the score. The answer here would be to make the evaluation interval very small, but the software only has a one-second resolution. So for benchmarks that run for only a few seconds (anyone benchmarking wPrime or SuperPi, for example), might either fail to be accelerated if the evaluation window is set at default, or only slightly when set at one second.

As you can imagine, if a reviewer does not know if TBM3 is enabled or not, there may be some odd benchmark results that seem different to what you might expect. It should be noted that because of the BIOS issue and the potential for motherboard manufacturers to do something different with every product, we ran our benchmarks with TBM3 disabled, and readers should check to see if reviewers specify how TBM3 is being used when data is published.

Package Differences: It’s Thin

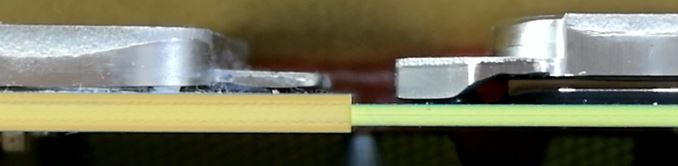

When the Skylake mainstream platform was launched, it was noted that the processor packages and substrates were thinner compared to the previous generation. It would appear that Intel is using the same packaging technology for Broadwell-E as well.

On the left is the Haswell-E based Core i7-5960X, and on the right is the Broadwell-E based Core i7-6950X. Both of these platforms use a FIVR, the Fully Integrated Voltage Regulator, which Intel equipped on this microarchitecture in order to increase power efficiency. Usually the presence of the FIVR would require additional layers for power management in the package, but it would seem that Intel has been optimizing this to a certain extent. Each individual layer is certainly thinner, but it is likely that Intel has also reduced the number of layers, though my eyes cannot discern the resolution needed to see exactly how many are in each CPU (and I don’t have a microscope on hand to test).

A couple of questions will crop up from readers regarding the thinner package. Firstly, on the potential for bending the package, especially in regards to a minor story on Skylake where a couple of CPUs were found to have bent when under extreme cooler force. As far as Intel is aware, Broadwell-E should not have a problem for a number of reasons, but mostly related to the dual latch socket design and socket cooler implementation. Intel’s HEDT platforms, from Sandy Bridge-E on, have been rated as requiring 30-40% more pressure per square inch then the mainstream platforms. As a result the sockets have been designed with this in mind, ensuring the pressure of the latch and cooler stays on the heatspreader.

The other question that would come to my mind is the heatspreader itself. Intel has stated that they are not doing anything new with regards to the thermal interface material here compared to previous designs, and it is clear that the heatspreader itself is taller to compensate for the z-height difference in the processor PCB.

If we compare the ‘wing’ arrangement between the Haswell-E and Broadwell-E processors, Intel has made the layout somewhat more robust by adding more contact area between the heatspreader and the PCB, especially in the corners and sides. One would assume this is to aid the thinner PCB, although without proper stress testing tools I can’t verify that claim.

205 Comments

View All Comments

Impulses - Tuesday, May 31, 2016 - link

Or just get a 5820K if you'd benefit from the extra cores... Or a 6600/6700K if you want the IPC bump for non gaming tasks and platform upgrades (USB 3.1, more lanes for M.2, etc).After throwing tick tock out the window it's unlikely the next refresh will be any more tempting. If you don't need any of the aforementioned things (more cores or platform upgrades) then you might as well sit tight tho.

rhysiam - Tuesday, May 31, 2016 - link

I've asked this question before and never got a good answer, so I'm trying again. Can someone explain to me why the boost clocks on the SKUs with more cores are always so much lower than those with fewer cores enabled?Base clocks have to be lower of course. I've got no issues with 10 active cores requiring lower clocks than 6 active cores, that makes sense. But what I don't get is why a 10 core SKU with 1 active core and 9 idle is somehow unable to turbo anywhere near as a 6 core implementation which is effectively 1 active core, 5 idle cores and 4 disabled cores on the same silicon . Is the power difference between those 4 idle & disabled cores really so significant on a 140W CPU that it necessitates an almost 10% lower clock speed?

It makes it even harder to justify spending $1.7K on a CPU when it looses so many benchmarks to CPUs costing a fraction of the price (including often the almost 3 year old 4820K).

RealLaugh - Tuesday, May 31, 2016 - link

I would like to know this too, I looked at the frequency and was surprised but I don't understand why it's like that.Also in the past Intel's top like Xeons have had hugh cache + core count but between 2-3GHz clock speeds only...

Ph0b0s - Tuesday, May 31, 2016 - link

Brief go at an explanation. Others can chime in to add on to my very simplistic explanation.The higher cored CPU's having lower clocks is down the to thermal envelope (referred to as TDW in watts) they are trying to hit on that CPU. Each core when working is effectively a heather on the CPU package. On CPU's with more cores, the heaters are more dense, i.e more heaters per area as they try to hit the same physical CPU package size whether 6 or 10 cores.

When all the cores are going a 10 core CPU will generate more heat than a 6 or 4 core CPU when the clocks are the same. To keep the 10 core CPU from hitting the thermal envelope limits that Intel put on them they decrease clock speed to offset the extra heat they are getting from the extra cores.

rhysiam - Tuesday, May 31, 2016 - link

Yes, but the "boost" clocks refer to single (or lightly) threaded workloads. Only one core is working. Your last paragraph refers to "when all the cores are going" - that's a base clock situation. As I said in my post I have no issue at all with 10 active cores requiring a lower frequencies than 6 in the same package. It's the single core taxed scenario I struggle to understand.adamod - Wednesday, June 1, 2016 - link

just a side note....my x5660's are rated at 2.8 base and 3.2 boost and with all 12 cores (dual socket setup) and 24 threads going 100 percent load and pulling 102W ea (while rated at 95W ea) mine NEVER get below 3.1ghz...i somehow got lucky as shit because i have two that can do it and only get to about 80C with the stock cooling on my hp workstation...sometimes you get lucky.....unfortunately i cant overclock though :(ThortonBe - Tuesday, May 31, 2016 - link

Perhaps it is like this. Not every transister has the same performance. When you increase the number of transisters (more cores) you increase the chance that you will get some slower transisters. For the turbo spec every core needs to be able to hit it.By making the turbo spec lower for higher core parts, Intel will have more parts that can be sold as the more expensive part (e.g. with ten cores they have a higher chance of fabricating a slow core than with six cores so they lower the max turbo on the ten cores to compensate to keep yields high).

Also, the floorplans (how the cores are wired up) might differ between the ten and eight core parts. In the GHz even the wiring can severely limit how high a frequency can be achieved. The more complex ten core designs are probably harder to wire up properly.

rhysiam - Wednesday, June 1, 2016 - link

The idea of tolerances with individual cores is an interesting suggestion I hadn't thought of.RE your last paragraph though, my understanding is that all 4 of these SKUs are identical chips, with the lower parts simply having cores (and PCIe lanes) disabled. That was certainly the case with Haswell-E CPUs and I'm assuming the same here. So the 10 core designs are exactly the same as the 6 core.

I suppose it's possible that the 6 core chips undergo testing and have their worst cores disabled, allowing higher turbo frequencies. It just seems, particularly with this generation, that the $1.7K flagship CPU is going to be such a low volume part anyway that they should be able to cherry-pick CPUs which can hit higher boost clocks.

Your suggestion would certainly explain why they're pursuing and promoting "turbo boost max 3.0." It seems like it's a bit of a mess at the moment, but if they can allocate single threaded workloads to the "best" core, surely they could start to hit much better boost clocks?

With Haswell the situation was even worse. You can buy a 4790K which can boost a single core to 4.4Ghz, but the best single threaded Haswell-E option (5930K), despite more the 50W additional TDP to play with and no iGPU for competition has to settle for a full 700mhz (16%) lower on the boost clock. I realise there's additional complexity with the "E" parts with larger cache and a wider memory bus, but that's a massive sacrifice to make that in many cases makes the cheaper 4790K the faster CPU, often by a wide margin.

I'd welcome other thoughts/comments/ideas here.

SAAB340 - Wednesday, June 1, 2016 - link

The 6950X will all have to be well binned to start with. They will all have to have the whole chip working and be able to do so at low voltage enough to meet the 140W TDP. If you have a leakier fully working chip it might still be sold as a 8 or 6 core version given that you just disable 2 or 4 (fully working but leaky) cores to meet the 140W TDP.The Turbo speed bins being lower in general the more cores you get on a CPU is certainly a function of that every individual core will have to be able to hit the highest turbo bin, even though it won't be TDP limited at that time. So you're pretty much guaranteed to be able to overclock to max single core turbo speed but you will most likely exceed the TDP.

It's just the same as that its way harder to find a hexa- octa- or deca-core chip able to reach xGHz overclock on all cores compared to finding a quad-core chip able to reach the same xGHz as 'only' 4 cores have to be good enough overclockers to reach it. The more cores, the less likely when we start to push the limits.

Turbo Boost Max 3.0 is certainly sounding like an interesting function where by the sound of it they instead try to identify the core that is able to run at the highest frequency. Here the opposite would be true, the more cores to choose from the higher likelihood to find one able to reach xGHz.

extide - Monday, June 6, 2016 - link

The floorplan does not differ. All 4 of these sku's use the exact same 10-core die. The lower end ones just have cores disabled, but otherwise they are the same exact silicon.