The Intel 6th Gen Skylake Review: Core i7-6700K and i5-6600K Tested

by Ian Cutress on August 5, 2015 8:00 AM ESTSkylake's iGPU: Intel Gen9

Both the Skylake processors here use Intel’s HD 530 graphics solution. When I first heard the name, alarm bells went off in my head with questions: why is the name different, has the architecture changed, and what does this mean fundamentally?

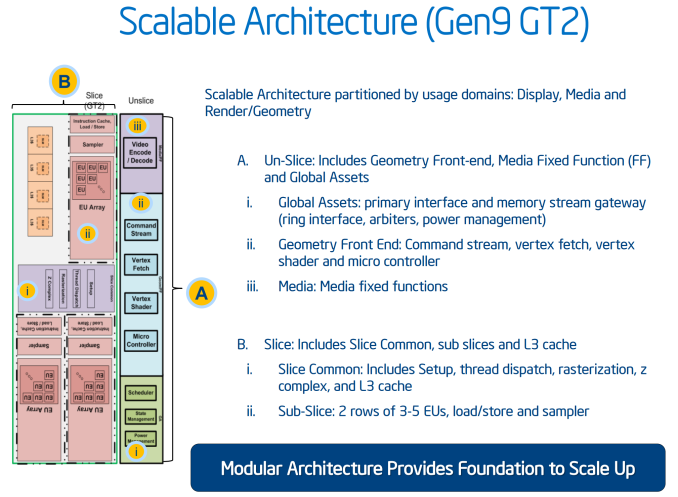

Not coming up with many details, we did the obvious thing – check what information comes directly out of the processor. Querying HD 530 via Intel's OpenCL driver reports a 24 EU design running at 1150 MHz. This is different than what GPU-Z indicates, which points to a 48 EU design instead, although GPU-Z is not often correct on newer graphics modules before launch day. We can confirm that this is a 24 EU design, and this most likely follows on from Intel’s 8th Generation graphics in the sense that we have a base GT2 design featuring three sub-slices of 8 EUs each.

As far as we can tell, Intel calls the HD 530 graphics part of its 9th Generation (i.e. Gen9). We have been told directly by Intel that they have changed their graphics naming scheme from a four digit (e.g. HD4600) to a three digit (HD 530) arrangement in order "to minimize confusion" (direct quote). Personally we find that it adds more confusion, because the HD 4600 naming is not directly linked to the HD 530 naming. While you could argue that 5 is more than 4, but we already have HD 5200, HD 5500, Iris 6100 and others. So which is better, HD 530 or HD 5200? At this point it will already create a miasma of uncertainty, probably exaggerated until we get a definite explanation of the stack nomenclature.

Naming aside, Generation 9 graphics comes with some interesting enhancements. The slice and un-slice now have individual power and clock domains, allowing for a more efficient use of resources depending on the load (e.g. some un-slice not needed for some compute tasks). This lets the iGPU better balance power usage between fixed-function operation and programmable shaders.

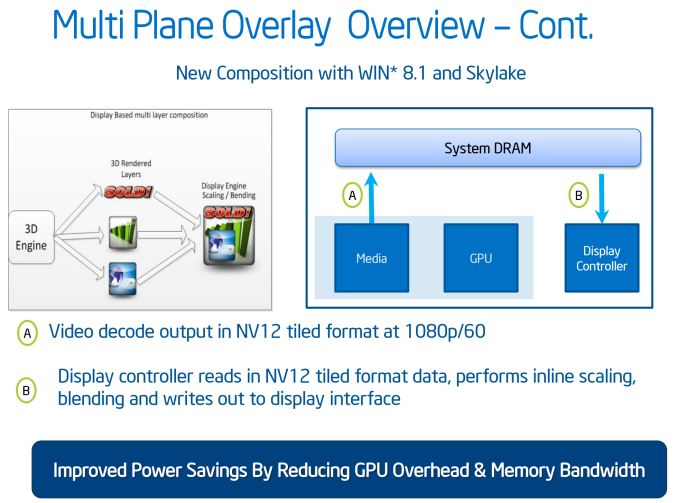

Generation 9 will support a feature called Multi Plane Overlay, which is a similar feature to AMD’s video playback path adjustments in Carrizo. The principle here is that when a 3D engine has to perform certain operations to an image (blend, resize, scale), the data has to travel from the processor into DRAM then to the GPU to be worked on, then back out to DRAM before it hits the display controller, a small but potentially inefficient operation in mobile environments. What Multi Plane Overlay does is add fixed function hardware to the display controller to perform this without ever hitting the GPU, minimizing power consumption from the GPU and taking out a good portion of DRAM data transfers. This comes at a slight hit for die area overall due to the added fixed function units.

As shown above, this feature will be supported on Win 8.1 with Skylake’s integrated graphics. That being said, not all imaging can be moved in this way, but where possible the data will take the shorter path.

To go along with the reduced memory transfer, Gen9 has support for memory color stream compression. We have seen this technology come into play for other GPUs, where by virtue of fixed function hardware and lossless algorithms this means that smaller quantities of image and texture data is transferred around the system, again saving power and reducing bandwidth constraints. The memory compression is also used with a scalar and format conversion pipe to reduce the encoding pressure on the execution units, reducing power further.

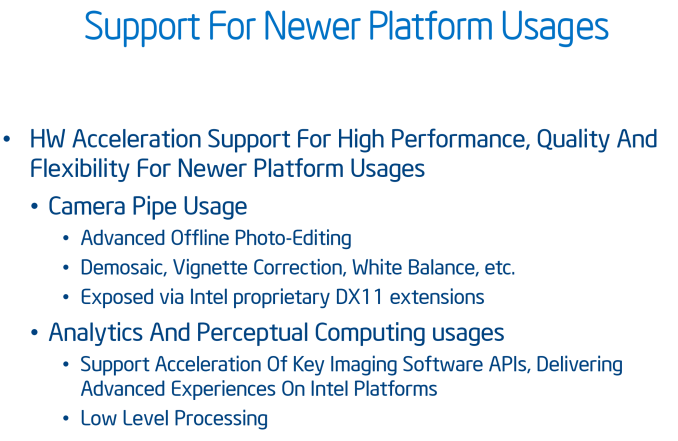

Adding into the mix, we have learned that Gen9 includes a feature called the ‘Camera Pipe’ for quick standard adjustments to images via hardware acceleration. This adjusts the programmable shaders to work in tandem for specific DX11 extensions on common image manipulation processes beyond resize/scale. The Camera Pipe is teamed with SDKs to help developers connect into optimized imaging APIs.

Media Encoding & Decoding

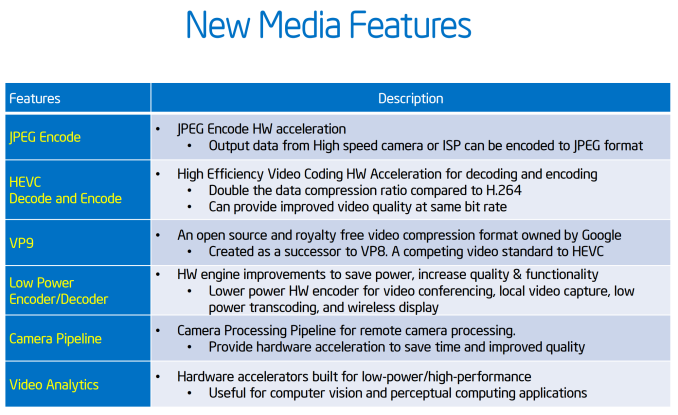

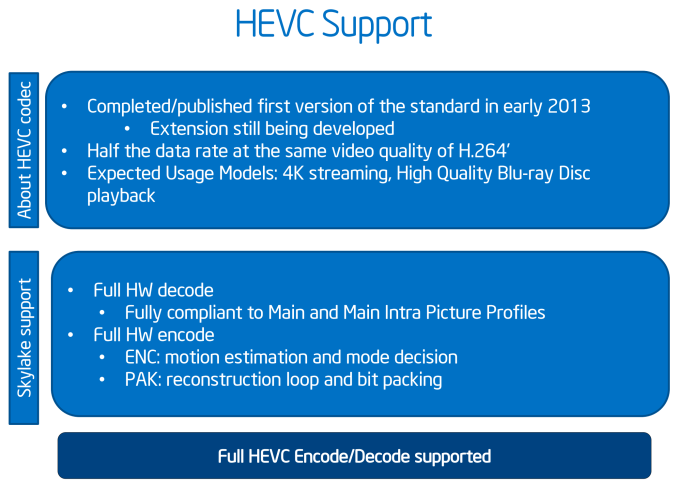

In the world of encode/decode, we get the following:

Whereas Broadwell implemented HEVC decoding in a "hybrid" fashion using a combination of CPU resources, GPU shaders, and existing GPU video decode blocks, Skylake gets a full, low power fixed function HEVC decoder. For desktop users this shouldn't impact things by too much - maybe improve compatibility a tad - but for mobile platforms this should significantly cut down on the amount of power consumed by HEVC decoding and increase the size and bitrate that the CPU can decode. Going hand-in-hand with HEVC decoding, HEVC encoding is now also an option with Intel's QuickSync encoder, allowing for quicker HEVC transcoding, or more likely real-time HEVC uses such as video conferencing.

Intel is also hedging their bets on HEVC by also implementing a degree of VP9 support on Skylake. VP9 is Google's HEVC alternative codec, with the company pushing it as a royalty-free option. Intel calls VP9 support on Skylake "partial" for both encoding and decoding, indicating that VP9 is likely being handled in a hybrid manner similar to how HEVC was handled on Broadwell.

Finally, JPEG encoding is new for Skylake and set to support images up to 16K*16K.

Video Support

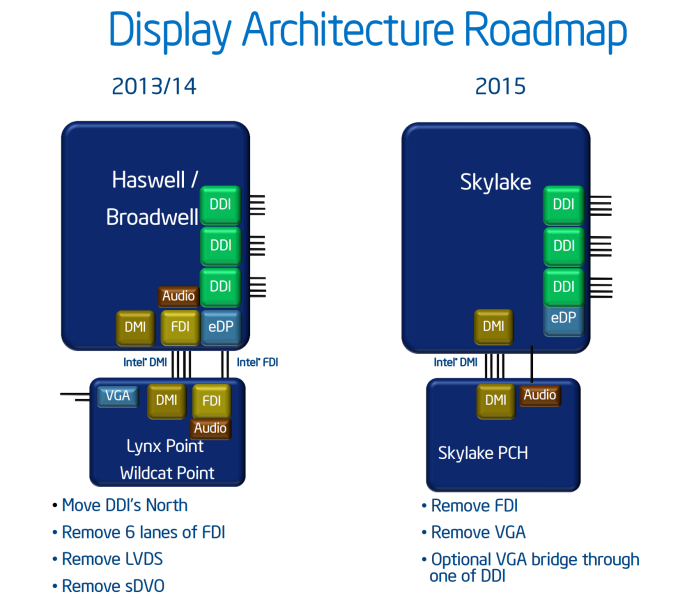

The analog (VGA) video connector has now been completely removed from the CPU/chipset combination, meaning that any VGA/D-Sub video connection has to be provided via an active digital/analog converter chip. This has been a long time coming, and is part of a previous committment made by Intel several years ago to remove VGA by 2015. Removing analog display functionality will mean added cost for legacy support in order to drive analog displays. Arguably this doesn’t mean much for Z170 as the high end platform is typically used with a discrete graphics card that has HDMI or DisplayPort, but we will see motherboards with VGA equipped in order to satisfy some regional markets with specific requirements.

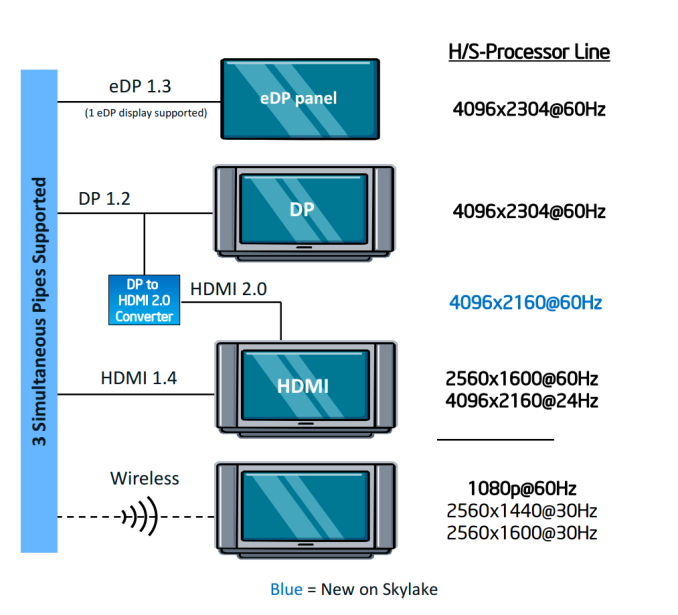

HDMI 2.0 is not supported by default, and only the following resolutions are possible on the three digital display controllers:

A DP to HDMI 2.0 converter, specifically an LS-Pcon, is required to do the adjustments, be it on the motherboard itself or as an external adapter. We suspect that there will not be many takers buying a controller to do this, given the capabilities and added benefits listed by the Alpine Ridge controller.

477 Comments

View All Comments

Modzy - Wednesday, August 5, 2015 - link

I'm still using my 2500K cruising along at 5.25Ghz. Unless skylake are nuts overclockers I think ill keep waiting a few more years.Refuge - Wednesday, August 5, 2015 - link

They aren't, but if you are running that daily, I'm impressed it is still running now, and if it still is in 3 years you better frame that bitch and hang it up in your office!What kinda cooler/mobo/psu are you running?

Bambooz - Wednesday, August 5, 2015 - link

@Refuce: How's that anything special? http://valid.canardpc.com/byk3u4Bambooz - Wednesday, August 5, 2015 - link

*Refuge .. dammitbernstein - Wednesday, August 5, 2015 - link

am i understanding correctly that DMI3 is just 4x8Gb/s = ~4GB/s compared to the 2.5GB/s we had with sandy bridge?thats not even enough for one PCIe3 x4 SSD... let alone a 3x PCIe x2 SSD RAID.

or when using one 10GbE & one USB3.1 we're basically still limited to PCIe2 x4 / PCIe3 x2

repoman27 - Wednesday, August 5, 2015 - link

DMI 3.0 x4 is essentially the same as PCIe 3.0 x4 from a bandwidth perspective, just as DMI 2.0 x4 was equivalent to PCIe 2.0 x4.DMI / PCIe 2.0 operate at 5.0 GT/s but use 8b/10b encoding which makes it 4.0 Gbit/s per lane.

DMI / PCIe 3.0 bump that up to 8.0 GT/s and switch to the more efficient 128b/130b encoding resulting in 7.877 Gbit/s per lane.

So the new DMI 3.0 x4 link is 31.5 Gbit/s, or roughly twice the bandwidth of DMI 2.0 x4 at 16 Gbit/s. Just as with previous PCH implementations though, the DMI is heavily oversubscribed. However, the fastest single port on the Z170 is PCIe 3.0 x4, so no devices will be bottlenecked by the DMI while operating individually.

jrs77 - Wednesday, August 5, 2015 - link

I'm really glad that I opted for the i7-5775C instead of waiting for Skylake. I don't need a couple of MHz more for the CPU, as even the 3.3GHz is more than enough for most of my workload. I need the best iGPU I can get tho, so I can built the smallest and most energy-efficient workstation possible.A workstation the size of a MacMini with a 3.3GHz 4C/8T CPU and an iGPU as powerful as a GT740 / R7 250 with only some 125W powerdraw under full load at the plug in the wall :)

Beaver M. - Wednesday, August 5, 2015 - link

This is one joke of an upgrade...Now I still cant decide if I take an i7-5775C, i7-4790K, i7-5820K or an i7-6700K.

Good job, Intel...

Teknobug - Wednesday, August 5, 2015 - link

Seems I'd be more included to buy an i7 5775C or i5 5675C than a Skylake I guess.Juggzz - Wednesday, August 5, 2015 - link

Thank you for the review, but what a pile of junk. What is Intel thinking?? Why are they releasing a product that can't even compete with their 4 year old processors?