The iPhone 5s Review

by Anand Lal Shimpi on September 17, 2013 9:01 PM EST- Posted in

- Smartphones

- Apple

- Mobile

- iPhone

- iPhone 5S

After Swift Comes Cyclone Oscar

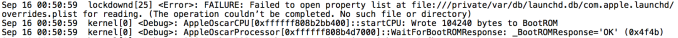

I was fortunate enough to receive a tip last time that pointed me at some LLVM documentation calling out Apple’s Swift core by name. Scrubbing through those same docs, it seems like my leak has been plugged. Fortunately I came across a unique string looking at the iPhone 5s while it booted:

I can’t find any other references to Oscar online, in LLVM documentation or anywhere else of value. I also didn’t see Oscar references on prior iPhones, only on the 5s. I’d heard that this new core wasn’t called Swift, referencing just how different it was. Obviously Apple isn’t going to tell me what it’s called, so I’m going with Oscar unless someone tells me otherwise.

Oscar is a CPU core inside M7, Cyclone is the name of the Swift replacement.

Cyclone likely resembles a beefier Swift core (or at least Swift inspired) than a new design from the ground up. That means we’re likely talking about a 3-wide front end, and somewhere in the 5 - 7 range of execution ports. The design is likely also capable of out-of-order execution, given the performance levels we’ve been seeing.

Cyclone is a 64-bit ARMv8 core and not some Apple designed ISA. Cyclone manages to not only beat all other smartphone makers to ARMv8 but also key ARM server partners. I’ll talk about the whole 64-bit aspect of this next, but needless to say, this is a big deal.

The move to ARMv8 comes with some of its own performance enhancements. More registers, a cleaner ISA, improved SIMD extensions/performance as well as cryptographic acceleration are all on the menu for the new core.

Pipeline depth likely remains similar (maybe slightly longer) as frequencies haven’t gone up at all (1.3GHz). The A7 doesn’t feature support for any thermal driven CPU (or GPU) frequency boost.

The most visible change to Apple’s first ARMv8 core is a doubling of the L1 cache size: from 32KB/32KB (instruction/data) to 64KB/64KB. Along with this larger L1 cache comes an increase in access latency (from 2 clocks to 3 clocks from what I can tell), but the increase in hit rate likely makes up for the added latency. Such large L1 caches are quite common with AMD architectures, but unheard of in ultra mobile cores. A larger L1 cache will do a good job keeping the machine fed, implying a larger/more capable core.

The L2 cache remains unchanged in size at 1MB shared between both CPU cores. L2 access latency is improved tremendously with the new architecture. In some cases I measured L2 latency 1/2 that of what I saw with Swift.

The A7’s memory controller sees big improvements as well. I measured 20% lower main memory latency on the A7 compared to the A6. Branch prediction and memory prefetchers are both significantly better on the A7.

I noticed large increases in peak memory bandwidth on top of all of this. I used a combination of custom tools as well as publicly available benchmarks to confirm all of this. A quick look at Geekbench 3 (prior to the ARMv8 patch) gives a conservative estimate of memory bandwidth improvements:

| Geekbench 3.0.0 Memory Bandwidth Comparison (1 thread) | ||||||

| Stream Copy | Stream Scale | Stream Add | Stream Triad | |||

| Apple A7 1.3GHz | 5.24 GB/s | 5.21 GB/s | 5.74 GB/s | 5.71 GB/s | ||

| Apple A6 1.3GHz | 4.93 GB/s | 3.77 GB/s | 3.63 GB/s | 3.62 GB/s | ||

| A7 Advantage | 6% | 38% | 58% | 57% | ||

We see anywhere from a 6% improvement in memory bandwidth to nearly 60% running the same Stream code. I’m not entirely sure how Geekbench implemented Stream and whether or not we’re actually testing other execution paths in addition to (or instead of) memory bandwidth. One custom piece of code I used to measure memory bandwidth showed nearly a 2x increase in peak bandwidth. That may be overstating things a bit, but needless to say this new architecture has a vastly improved cache and memory interface.

Looking at low level Geekbench 3 results (again, prior to the ARMv8 patch), we get a good feel for just how much the CPU cores have improved.

| Geekbench 3.0.0 Compute Performance | ||||||

| Integer (ST) | Integer (MT) | FP (ST) | FP (MT) | |||

| Apple A7 1.3GHz | 1065 | 2095 | 983 | 1955 | ||

| Apple A6 1.3GHz | 750 | 1472 | 588 | 1165 | ||

| A7 Advantage | 42% | 42% | 67% | 67% | ||

Integer performance is up 44% on average, while floating point performance is up by 67%. Again this is without 64-bit or any other enhancements that go along with ARMv8. Memory bandwidth improves by 35% across all Geekbench tests. I confirmed with Apple that the A7 has a 64-bit wide memory interface, and we're likely talking about LPDDR3 memory this time around so there's probably some frequency uplift there as well.

The result is something Apple refers to as desktop-class CPU performance. I’ll get to evaluating those claims in a moment, but first, let’s talk about the other big part of the A7 story: the move to a 64-bit ISA.

464 Comments

View All Comments

A5 - Wednesday, September 18, 2013 - link

I don't think anyone does GPGPU on phones yet. Android has some extremely experimental OpenCL support, but it hasn't been on a shipping device yet. Physics on phones is still a purely CPU-driven affair.bod - Wednesday, September 18, 2013 - link

M7 is outside, because if it were inside, there would be too much leakage current in the A7 even if the rest of the SoC was power gated. I suppose :)debacon - Wednesday, September 18, 2013 - link

A thorough review. Great help in eliminating many questions when trying to make the choice for upgrade, or outright purchase. Thank you.supergex - Wednesday, September 18, 2013 - link

Tired of seeing comparisons with Android or other Apple products. Don't you think a couple of the best Windows Phones or even Blackberry could have some room over here?darwiniandude - Wednesday, September 18, 2013 - link

Yeah, may as well compare Palm OS and Symbian while you're at it.Gridlock - Wednesday, September 18, 2013 - link

I'd be curious to see if either has any attributes that define or differentiate it (cellular talktime or performance on the Blackberry or photography on the Nokia for instance).I suspect, at least as far as BB goes, the answer is probably 'no'.

Eug - Wednesday, September 18, 2013 - link

"First off, based on conversations with as many people in the know as possible, as well as just making an educated guess, it’s probably pretty safe to say that the A7 SoC is built on Samsung’s 28nm HK+MG process. It’s too early for 20nm at reasonable yields, and Apple isn’t ready to move some (not all) of its operations to TSMC."Anand, how sure are you that it is Samsung? The chip numbering on the A7 is different according to teardowns of leaked parts, which caused some to speculate that it is a TSMC part.

Judging by analyst rumours, Samsung still makes sense to me for the A7 (with maybe A8 or other chips going to TSMC), but I'm just curious.

ettohg - Wednesday, September 18, 2013 - link

So, I just had to check, sorry.In the iPhone 5 review, posted on October 16, 2012, the iPhone 5 had a score in Kraken that was 19618 . In this review, the iPhone 5 has a score of 13919 .

In the previous review, the iPhone 5 also had a score of 1672 in the Google Octane Benchmark v1, while in this review the iPhone 5 has a score of 2859.

I also checked, it's the same software version. Is something wrong here?

Maybe the improvements are not from the chip architecture but from iOS 7 ?

Also, are you *honestly* telling me that you repeated ALL the tests with the iPhone 5 instead of just copying-pasting the results?

thunng8 - Wednesday, September 18, 2013 - link

iPhone5 also benefits from improved software. You'll notice 5s results are much higher than the 5 as well.robinthakur - Wednesday, September 18, 2013 - link

Don't try to explain it to them with facts, it's like the South Park episode "Simpsons Did It" I appreciate the innovation from the 5s and it guarantees that Apple will receive the £600 yearly iPhone renewal once again when I sell my 5.