Ask the Experts: ARM's Cortex A53 Lead Architect, Peter Greenhalgh

by Anand Lal Shimpi on December 10, 2013 9:00 AM EST- Posted in

- Ask the Experts

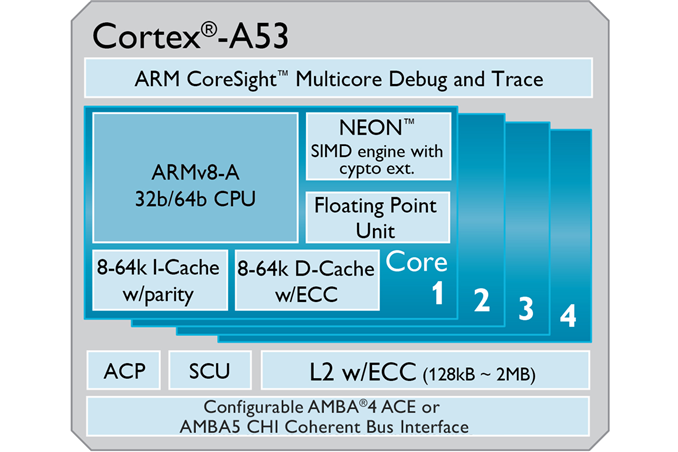

Given the timing of yesterday's Cortex A53 based Snapdragon 410 announcement, our latest Ask the Experts installment couldn't be better. Peter Greenhalgh, lead architect of the Cortex A53, has agreed to spend some time with us and answer any burning questions you might have on your mind about ARM, directly.

Peter has worked in ARM's processor division for 13 years and worked on the Cortex R4, Cortex A8 and Cortex A5 (as well as the ARM1176JZF-S and ARM1136JF-S). He was lead architect of the Cortex A7 and ARM's big.LITTLE technology as well.

Later this month I'll be doing a live discussion with Peter via Google Hangouts, but you guys get first crack at him. If you have any questions about Cortex A7, Cortex A53, big.LITTLE or pretty much anything else ARM related fire away in the comments below. Peter will be answering your questions personally in the next week.

Please help make Peter feel at home here on AnandTech by impressing him with your questions. Do a good job here and I might be able to even convince him to give away some ARM powered goodies...

158 Comments

View All Comments

shing3232 - Tuesday, December 10, 2013 - link

A7 usually have almost same performance as A8 although with less execution resource, but A7 have a much more efficient BPUTechguy99X - Tuesday, December 10, 2013 - link

What is the main difference in A5, A7, A9, A12, A15, A53 and A57 for single threaded performance? Is it still worth having 4+4 big.LITTLE compared to 8x A7 ?archgeek - Tuesday, December 10, 2013 - link

1. Do you think that cortex A12 should have been announced earlier(as the gap between A9 and A15 was huge and something in between those two was required) ?2. Similar to A12, Will there be anything in between A53 and A57 in near future?

3. Instead of using big.LITTLE config and putting 8 cores(4 A15 and 4 A7), why can't we have efficient power gating and other innovative techniques inside the high performance cores so that they can be run as efficient as A7 cores. Die area of individual A15 will increase but we can save some total area as only 4 A15 will be required. How difficult it is from architecture point on view?

MrSpadge - Tuesday, December 10, 2013 - link

The answer is the same as to "Why can't Intel put a Haswell into my phone?" When you need T transistors to implement some functionality in some basic way you might get performance P at power consumption Q. Implement some clever trick which increase performance to 1.5*P. This will probably require more than 1.5*P transistors, probably more like 2*P. And hence power consumption will increase to approximately 2*Q as well. And you can't power-gate this additional power draw because you actually need those transistors to work in order to perform the desired function.That's why building ever more complex single cores comes at the price of power efficiency.

barleyguy - Tuesday, December 10, 2013 - link

When designing a processor and deciding on which performance attributes to emphasize, do you target current workloads for short term market concerns, or do you target possible future workloads for the market a year or two from now? Or is performance tuning more workload agnostic, and do you say "I want this to be fast for everything"?For example, since ARM processors are very popular in the Android market, do you tune for content comsumption and gaming? Or since Android may be trending towards more of a primary computing device in the future, is it important to tune for desktop applications?

And finally, what are the considerations of performance tuning for thermally constrained devices?

Peter Greenhalgh - Wednesday, December 11, 2013 - link

Hi Barleyguy,A good question. A general purpose processor has to be good on all workloads. After all, we expect to see Cortex-A53 in everything from mobile phones to cars, set-top-box to micro-servers and routers. However we do track the direction software is evolving – for example the increased use of Javascript which puts pressure on structures such as indirect predictors. Therefore we design structures within the processor to cope with future code as well as existing expected workloads.

psychobriggsy - Tuesday, December 10, 2013 - link

Do you have any plans to support various forms of turbo functionality within your next generation ARM cores? An a potential example, in a 28nm quad-core A53 setup at 1.2GHz, you could support dual-core at >1.4GHz and single core at >1.6GHz within the same power consumption (core design allowing, of course), yet single threaded performance could improve significantly.ARM cores have been historically low power, however that doesn't mean there aren't more power savings to be made. Examples include deeper sleep states, power gated cores, and so on - features that Intel and AMD have had to include in order to reduce their TDPs whereas ARM cores haven't need them (yet). What are the future power saving methods that ARM is considering for its future cores (that you can give away)?

Peter Greenhalgh - Wednesday, December 11, 2013 - link

Hi Psychobriggsy,A Turbo mode is typically a form of voltage overdrive for brief periods of time to maximise performance, which ARM partners have been implementing on mobile platforms for many years. Whether this is applied to 1,2 or more cores is a decision of the Operating System and the platform power management software. If there is only one dominant thread you can bet that mobile platforms will be using Turbo mode. Due to the power-efficiency of Cortex-A53 on a 28nm platform, all 4 cores can comfortably be executing at 1.4GHz in less than 750mW which is easily sustainable in a current smartphone platform even while the GPU is in operation.

In terms of further power saving techniques, power gating unused cores is a technique that has been used since the first Cortex-A9 platforms appeared on the market several years ago. The technique is so fundamental that I think many in the mobile industry use it automatically and forget that it’s a highly beneficial power saving technique. But you are correct that there is more milage to come from deeper sleep states which is why both Cortex-A53 and Cortex-A57 support state retention techniques in caches and the NEON unit to further improve leakage power.

gregounech - Tuesday, December 10, 2013 - link

We see Qualcomm winning most designs these days with their implementation of ARM's ISAs, does ARM wish to bring back their own architecture (not just the ISA) to the front line of mobile products (consumer ones) ?What is your view on Intel newest mobile architecture BayTrail and how do you see Intel (and others) competing with ARM on the consumer grade mobile products in the near future ?

adrian_sev - Tuesday, December 10, 2013 - link

Are there any plans for desktop/server designs for ARM cpus? (i mean with pci-e lanes, ddr4 controllers, strong FPU (AVX2 like), without baseband logic and any other bloat hardware).If yes, is there a time frame?

Thank you!