Intel’s New IDM 2.0 Strategy: $20b for Two Fabs, Meteor Lake 7nm Tiles, New Foundry Services, IBM Collaboration, Return of IDF

by Dr. Ian Cutress on March 23, 2021 5:00 PM EST- Posted in

- CPUs

- Intel

- GPUs

- IBM

- 7nm

- Fab 42

- Chiplets

- Pat Gelsinger

- Meteor Lake

- IDF 2021

The new CEO of Intel, Pat Gelsinger, has today outlined his vision for Intel over the coming years. During an online presentation entitled ‘Intel Unleashed: Engineering The Future’, Pat Gelsinger outlined five key topics upon which Intel will work towards and what it means for the company at large. At the center of this is a reaffirmed commitment for Intel to retain its own fabs, but also double down on its ability to drive the latest technologies at scale by building new manufacturing facilities inside the US.

Highlights of Intel’s Announcements Today

- Two new fabs in Arizona, $20b investment

- New Intel Foundry Services, offering Intel manufacturing to customers

- Next generation 7nm chiplets for ‘Meteor Lake’ will finish design in Q2 2021

- New research collaboration with IBM in foundational semiconductor design

- New Intel Innovation event in Oct 2021, Spirit of IDF

We're Keeping the Fabs: Please Stop Asking

Since the start of the year, previous Intel CEO Bob Swan and new Intel CEO Pat Gelsinger have both done the equivalent of shouting from the rooftops when it comes to Intel’s market advantages. At the top of that list is Intel’s vertical integration between manufacturing and chip design, enabling Intel to control the process from top to bottom more closely than any of its chip competitors. This unique proposition labels Intel as an IDM (integrated device manufacturer) or having an IDM model (integrated device manufacturing model), and the only company that can even come close to Intel in this regard is Samsung. Intel’s plus over its competitor here is that it can apply its own designs to a scale that Intel is often attributed to.

In recent months there have been comments from analysts and investors about the potential for Intel to spin out its manufacturing plants and facilities into a separate business, similar to how AMD detached its manufacturing facilities into a new company called GlobalFoundries. The benefits of this move would allow Intel to segregate the losses between the two sides of the business, and showcase the core Intel product teams in a better light by comparison to the manufacturing arm. This sort of path has significant pitfalls, most importantly that Intel’s manufacturing main customer is Intel. GlobalFoundries had this problem initially, but Intel’s foundry arm is on a much larger scale.

So to that end, Pat Gelsinger today is hoping to put those rumors to rest, more than he stated on Intel’s 2020 financial call. Not only is Intel going to retain its manufacturing facilities, but it is going to embrace a new era of manufacturing, which is going to be called IDM 2.0.

IDM 2.0: Build, Expand, and Productize

This direction from Intel is built upon, first and foremost, the enthusiasm of Pat Gelsinger rejoining the company. Since even before he took over the role of CEO, former Intel engineering experts were coming out of retirement to work on exciting new products with Pat at the helm.

IDM 2.0 will have several pieces to the puzzle.

Build (7nm)

Today Intel will be announcing a $20 billion (USD) investment in two new manufacturing facilities (fabs) in Arizona, set to come online for production in 2024. Gelsinger will point out today that Intel is ready to break ground, increasing the number of factories on Intel’s Ocotillo campus (Chandler, AZ) from four to six.

These new fabs will be on leading edge process node technologies, with Intel extending cooperation with the State of Arizona, as well as the current administration’s target of improving semiconductor manufacturing inside the country. All parties involved seem raring to go, and Intel will be seeking to outfit its production facilities with the equipment necessary to enable leading edge manufacturing, including using Extreme Ultra Violet (EUV) technology.

Intel's Ocotillo campus, Fab 42, Chandler AZ

It is noteworthy that the machines that enable EUV manufacturing are only supplied by a single company, ASML, and demand for these machines is at a record high, with a waiting list of over a year. Intel believes that its technology, with its increasing use of EUV to simplify manufacturing and enabling higher performance and higher yielding products, will be fully aligned and there will be enough EUV to go around by the time these new fabs are up and running.

The two new fabs are expected to bring 3000+ high wage jobs direct with Intel, 3000+ construction jobs for construction during the project, and up to 15000 long-term ecosystem support jobs for the area. Planning for construction activities are expected to start immediately. That being said, TSMC has also indicated plans to build a factory in Arizona as well, likely in the Phoenix area, with Samsung also considering a site there (or Austin, TX). There have been questions as to the sustainability of supporting that many semiconductor manufacturing plants in a single city. Intel states that it already recycles 9 million gallons (US gal.) of water each day, and the company purchases green power for its facilities, as well as on-site alternative energy projects.

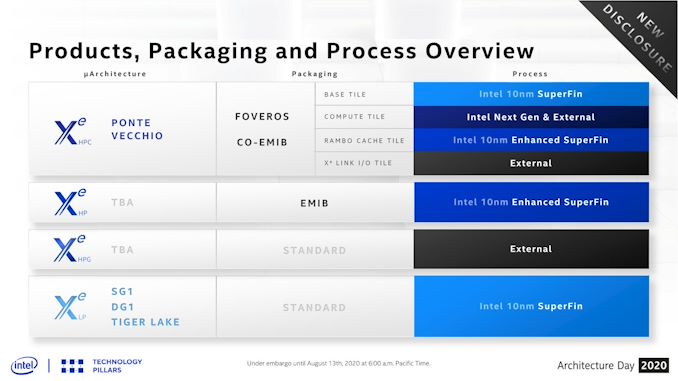

As part of this side of the announcement, Pat Gelsinger will be stating today that the 7nm manufacturing node from Intel is now running on schedule, with a solid footing. The first product enabled with 7nm will be Ponte Vecchio, the upcoming high-performance compute accelerator for the Aurora supercomputer, however end-users might be more interested in Meteor Lake, a client CPU compute tile for a volume 2023 product. Intel will announce today that the compute tile / chiplet will finish tape-in (design IP verification) by Q2 2021, and will leverage Intel’s advanced packaging techniques. After design manufacturing, tape-out (whole chip design verification) usually takes 4-6+ months, and then the designs are sent to the fabs for initial production and test runs. Given that Intel is talking about Meteor Lake as a chiplet design, starting with this compute tile, then no doubt an IO related chipset will be announced at a later time. Intel has a number of packaging technologies it could deploy here, such as EMIB or Foveros, depending on the cost intercept of the intended market.

Edit: Gelsinger confirmed that Meteor Lake will have Foveros technology.

Expand (TSMC)

Alongside building new manufacturing facilities, Intel today will reaffirm its roadmap to use a mixture of internal and external process node manufacturing depending on the product capabilities. Intel already makes heavy use of external partners, such as TSMC, and already spends enough to account for 6-7% of TSMC's annual revenue. But today’s announcement will double down on ensuring that Intel is ready to use the right process at the right time for the right products.

This includes developing its leading edge products on external foundry offerings. As Intel moves more into a chiplet ecosystem (Intel is calling it ‘tiles’), the company is prepared to manufacture its high-performance computing chiplets on external foundries. This means in both client and the datacenter, and likely means we will be seeing the latest x86 cores enabled beyond Intel. Exact announcements will follow.

Gelsinger’s presentation today will discuss that using external partners like TSMC, Samsung, GlobalFoundriers, and UMC, will allow the company to optimize roadmaps for cost, performance, schedule, and supply. This does somewhat go against the grain of the IDM 2.0 messaging, where Intel can control its own supply chain and expand production as required, however Intel expects it can find a happy medium.

Productize (IFS)

The two new manufacturing plants / fabs also filter under this Expand section, however this area is more focused on how Intel will keep those fabs fully occupied. Other semiconductor manufacturers in the market, such as TSMC, Samsung, GlobalFoundries, SMIC etc, they all have what are called foundry services which allow customers to build silicon using their manufacturing technology. With today’s announcement, the company is ready to enable its external Intel Foundry Services (IFS) to new customers. IFS will be a standalone company, with unique access to Intel's current and future offerings.

Intel has made silicon for others before, so this isn’t new. However, that project came at a time where Intel’s 10nm faltered, and the company lost a number of high-profile contracts with partners as a result. One of the issues is that Intel at the time used so many customized software tools in its silicon design process that it limited its customers’ access to these tools to build processors. This made the whole process very complicated.

The new Intel Foundry Services look will be a lot different. Intel today will have partnership announcements with Cadence and Synopsys to enable industry standard design tools (EDA tools) and workflows such that customers can use industry standard process development kits (PDKs) to build their silicon designs. This is part of the job that some of Intel’s hires have recently been enabling, such as Renduchintala, Keller, and Koduri. Intel is committing to embracing the entire EDA ecosystem to ease new customers into the use of Intel’s foundry tools.

There will be somewhat of a black cloud over Intel on how its external foundry offerings have failed in the past, however Gelsinger and the company are hoping that commitments to industry standards will help on that path to rebuilding trust and reputation.

As part of Intel’s Foundry Services, the company is announcing that it will work with customers to build SoCs with x86, Arm, and RISC-V cores, as well as leveraging Intel’s IP portfolio of core design and packaging technologies. What will be key here is the extent of exactly how Intel will offer its x86 designs – it could offer them in a licensing style similar to Arm, allowing customers to go build their own SoCs, or it could be only in a custom design services model, where you tell Intel what you want and they design/manufacture it for you. More details about how this will work is expected to come through the year.

The drive into Foundry Services is an obvious choice for Intel. Demand for semiconductor manufacturing is at an all-time high, and discussions about keeping manufacturing inside the US has been a key talking point for over a year. Intel has stated that it has keen enthusiastic support from the industry for IFS, but it will also disclose later in the year how it will expand its manufacturing capabilities in other parts of the world, such as Europe.

Collaboration with IBM, New Intel Events for Engineers

Alongside the core IDM 2.0 path, Intel also has announcements relating to the future of its R&D roadmap, as well as its outreach to engineers and commercial partners.

The collaboration with IBM on process node development and development of next-generation logic is the wildcard of today’s announcements. The two companies are set to work together on foundational technologies to move the needle on both semiconductor performance and semiconductor efficiency. The collaboration will scale through to the ecosystem, with a significant nod towards key US government initiatives.

Intel’s announcement today on this is light on details. The teams from both Oregon and New York would seem to initially start separate with collaboration-at-a-distance, although the nature of the wording of the announcement would seem to suggest that the two will come together with a semi-unified team at a later date. Intel is keeping details on the topics for research at a very high-level, but both companies have a range of expertise on fundamental silicon design as well as complex manufacturing. This might also be a nod to IBM getting access to Intel’s leading edge technologies for its POWER and z product offerings.

Also on the cards is Intel’s new series of events for engineers and commercial partners. Broadly marketed as Intel’s *on series, Gelsinger aims to rekindle the spirit behind Intel’s previous popular events such as Intel’s Developer Forum (IDF) with a new range of Intel Vision (commercial) and Intel Innovation (engineering) outreach.

The first of these events will be an Intel Innovation Event, coming in October later this year in San Francisco. If we are travelling to events again, no doubt we will be there to report on the highlights of Intel’s strategy at that point of time.

Pat Gelsinger’s Intel Legacy: Part One

Over the many interviews that Gelsinger has given over the years, his love of Intel is a persistent thread. Having finished his degree at the early age of 18, he was hired straight out of college and spent over 30 years at the company, reaching the title of Chief Technology Officer. Gelsinger then spent 12 years at EMC (now Dell EMC) and VMWare, and has come back as CEO. The hiring of an engineer at the top of the company has, in Intel’s own words, reinvigorated the enthusiasm of its engineering base.

It’s no secret that while Intel has been rewarded with record revenues these past five years, the state of play of Intel’s manufacturing roadmaps have stalled. Intel’s future has been in flux, affecting employees and followers of the company alike, leading to many column inches about how the company moves forward. The announcement of Pat Gelsinger to the role of CEO, plus his remarks during Intel’s FY2020 call, seems to have lit a fire inside Intel. Today’s announcements are the first stage in Pat Gelsinger building his CEO legacy at the company.

Intel’s path with the announcements today is very much towards a more flexible Intel. In the past where the company was rigid with its designs, rigid with its manufacturing, it is clear that Gelsinger wants to be more open and accepting of industry standard manufacturing whilst at the same time re-offering its facilities to external customers. The mantra of Intel staying on Intel manufacturing also seems to dissolve slightly, with Gelsinger not afraid to mention the name of other foundry offerings that Intel is prepared to use.

Our discussions with employees at Intel who know Pat Gelsinger have repeatedly said that he likes to ‘geek out’ over the details of new technology, and will happily sit for hours talking about both the direction of the industry as well as how Intel is positioned alongside its competition. Pat, if you’re reading this, we’re ready to geek out whenever you are.

159 Comments

View All Comments

rahvin - Thursday, March 25, 2021 - link

Ah baloney. The only ARM server processors even available only fit a certain niche. ARM has made incremental improvements with each generation, but AWS's Graviton was the first viable server processors and we have no idea what kind of economics are involved because AWS could be choosing to loose money on the processor to gain market-share and experience.The fact is you can't buy a ARM server right now that will be competitive with x86 in every category. Yes there are a couple options that work in certain situations but the TCO is still out of wack and IMO non-viable against x86, particularly with the strides AMD has made with Zen.

If servers still relied only on Intel I have no doubt ARM would be a much more viable competitor but that's simply not the case.

lmcd - Monday, March 29, 2021 - link

Licensed Atom Cores will crush low-end ARM, and high-end ARM hasn't actually proven to be efficient.nfineon - Thursday, March 25, 2021 - link

This is very good info to keep in mind thanks for posting the timelines. Gelsinger would ultimately have to sign off on the terrible pricing of the 11th gen high end sku's as well where at the top end Intel are trying to price an 8 core part with worse performance, thermals, and power against AMD's 12 core part which also has a slightly lower MSRP. The ultimate decision to push that absurd pricing must be signed off from the top.Bluetooth - Thursday, March 25, 2021 - link

Who would want to license x86 for future CPU, when ARM is available with better ISA. Is backwards compatibility in old software that important? Or would the licence just the x86-64 commands (which I think AMD has something to say in). Wouldn't someone licensing x86 get rid of the old 32 bit compatibility and just support 64 bit?rahvin - Thursday, March 25, 2021 - link

There is no ISA advantage for ARM. It's a BS talking point that has no basis in reality. x86 processors haven't used x86 internally in more than 20 years. Every x86 processor uses an internal flexible RISC core and tacks a 128k transistor translator on to handle the conversion from x86 to the internal language. That translator was a big part of the processor 20 years ago, today it's not even 0.01% of the die.If anything, the x86 translator actually gives the advantage to x86 because every single x86 processor can have a custom designed RISC core that is optimized for each process node.

proflogic - Friday, March 26, 2021 - link

That is a rather disingenuous argument. One of the ISA's biggest impacts is on instruction decoding, and you're simply ignoring it by waving away all the stages that happen before it becomes RISC-like internally. The variable-length instructions in x86 make it exceedingly difficult to avoid longer pipelines for decoding or to achieve a greater issue rate at high frequency. You blow through power and area searching for the ends of instructions and doing that translation, and the cost of any pipeline flush ends up being higher.One mitigating factor may be that code size (and cache pressure) is reduced there, but I'm fairly certain various papers have argued those benefits are pretty small against ISAs with a compressed format for common instructions.

Shorty_ - Tuesday, March 30, 2021 - link

this is precisely how it was explained to me by someone who built processors for a living.quiksilvr - Tuesday, March 23, 2021 - link

Phoenix has the largest nuclear power plant in the country, it does not snow there and land is relatively cheap for being the fifth largest city in the country. It is the perfect place for fabs.FreckledTrout - Tuesday, March 23, 2021 - link

As long as there are not to many to overwhelm water needs.JCB994 - Wednesday, March 24, 2021 - link

Last time I was there most of Arizona is sitting on a huge water aquifer. I could not believe paper plants were in the desert south of Phoenix but it is due to the water.