Chips&Media Launches Wave510A Hardware AV1 Decoder IP

by Anton Shilov on October 21, 2019 8:00 AM EST

Chips&Media this month has started to license out its Wave510A hardware decoder IP, the industry’s first AV1 video decoder. The base decoder core supports decoding up to 4Kp60, but it can be scaled out to handle 4Kp120 and 8Kp60 resolutions as well. The IP is designed to be integrated into SoCs for various applications, including televisions, STBs, smartphones, and PCs. Meanwhile, since the Wave510A only decodes AV1 streams, it will likely be licensed by parties who want to add AV1 to their existing SoCs.

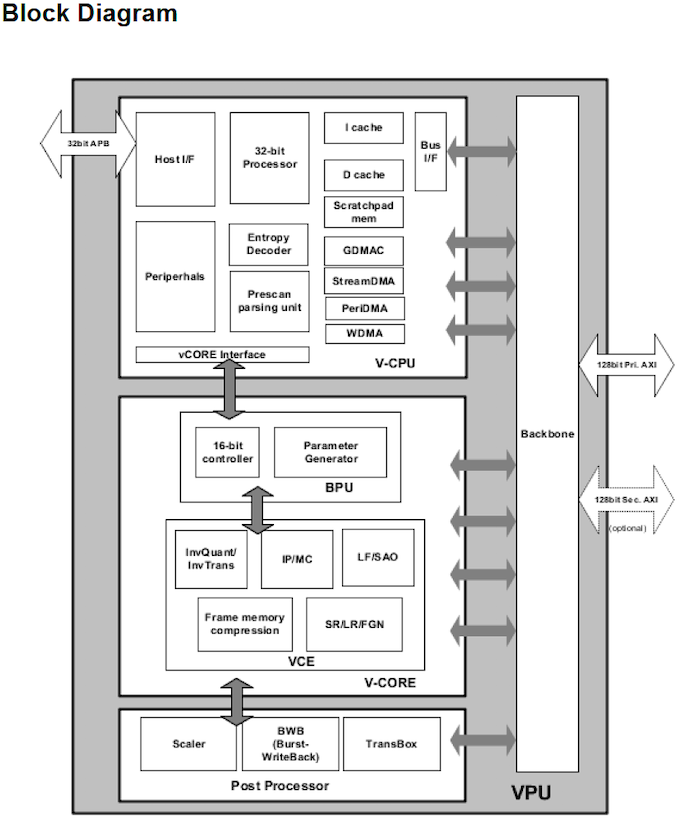

The Wave510A video processing unit (VPU) IP is based on two fundamental units: the V-Core and the V-CPU. The 32-bit V-CPU controls the whole IP block, communicates with host CPU, parses bitstream syntax from sequence to slice header unit, and prescans slice data. The V-Core performs entropy decoding, inverse scan, inverse transform/quantization, motion compensation, and loop filtering. The IP VPU can be connected to host using Arm’s 32-bit AMBA3 APB bus, and also has two 128-bit AMBA3 AXI busses to access external memory and on-chip SRAM.

The Chips&Media Wave510A can decode AV1 Main profile @ L5.1 50 Mbps at 8 or 10-bit color depths, with 4:2:0 chroma subsampling. The VPU can output to various displays at up to 8192x8192 resolution in various formats. When clocked at 500 MHz, it can support up to 4Kp60 realtime decoding in a single-core configuration, whereas in a dual-core configuration it can decode 4Kp120 and 8Kp60 streams.

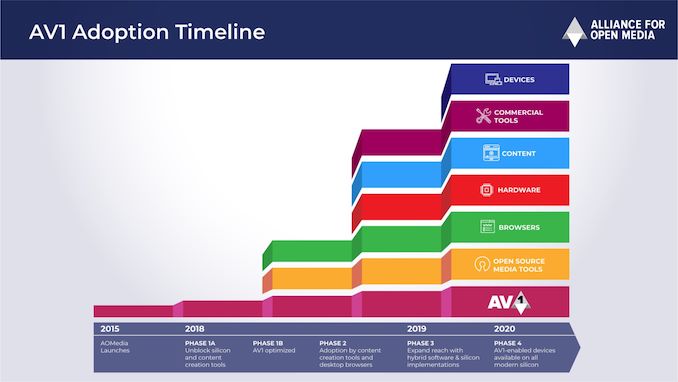

The AV1 royalty-free codec was introduced about 1.5 years ago by the Alliance for Open Media (AOMedia), and it is gaining traction throughout the industry. Over the past few months we have seen multiple technology licensing companies announcing hardware encoder IP blocks as well as several SoCs that already support AV1 decoding using in-house developed IP (or using general-purpose cores).

Amphion Semiconductor was the first company to announce an AV1 decoder with its CS8142 decoder IP, but this part is still in development. By contrast, the Wave510A from Chips&Media is available now and can licensed in the form of a verified synthesized RTL source. Meanwhile, the Wave510A only supports AV1, so to build a complete video decode pipeline supporting codecs like HEVC and AVC, designers will have to license or develop additional IP blocks to support those other codecs. On the other hand, the Wave510A can be easily added to existing designs and improve their feature set.

Related Reading:

- YouTube, Netflix Publish First Videos Transcoded Using AV1

- Alliance for Open Media Releases Royalty-Free AV1 1.0 Codec Spec

Source: Chips&Meida (via Design & Reuse)

24 Comments

View All Comments

GreenReaper - Monday, October 21, 2019 - link

It's not ideal for pixel-perfect graphics, but things like movies, TV shows and webcams typically use it, and I imagine that is the kind of purpose that this decoder is aimed towards.If you were streaming a game you might prefer 4:4:4, but you'd also want to do it in real-time. This is technically possible now, but it'll surely impact the game as well. Realistically most will wait for use a hardware encoder - or an entirely separate system, but how many will get one just for AV1? The most immediate benefit is for the companies for whom 4:2:0 is perfectly acceptable.

nirolf - Tuesday, October 22, 2019 - link

Thank for the explanation! It's enough for 4K HDR also?nevcairiel - Wednesday, October 23, 2019 - link

Practically all consumer video content is 4:2:0, including UltraHD Blu-rays in 4K HDR, or Netflix HDR streaming, or.. you name it. So, yes.Adonisds - Wednesday, November 27, 2019 - link

I think probably not because HDR uses 10 bits and that requires 4x more power to decode